| Page |

N° |

Poids |

Eléments de corrigé |

1

|

1a |

0,7

|

Technique CM2/P23 ou simplement 28=7x4=7<<2...

Et justement, pour

Booth, 7=8-1, équivalent à la règle 1 de CM8/P22 et PC9/Q1c.

Au fait, ce sont des entiers 8 bits, donc on veut voir 8 bits exactement. |

| 1b |

0,7

|

La méthode binaire idoine est le complément à 2 : cf. CM2/P28

& PC2/Q1b. Conformément à la consigne "trace", il fallait montrer le calcul, c'est-à-dire l'addition du complément à 1 avec l.

|

| 2a |

1

|

cf. PC4/Q1h, avec une petite contrainte supplémentaire sur le

placement des variables. |

| 2b |

1

|

FDM(f) = du+q'u+h'qd+hq'd'

Non regroupements de 1 en sous-cubes maximaux évidemment

sanctionnés, car forme alors non minimale. Tellement pratiqué au cours des PC ES102 qu'il est anormal de ne pas avoir 8/8

à une telle question. |

| 3 |

1

|

cf. CM1/P22 |

| 4 |

1

|

Les amateurs de Booth ont immédiatement reconnu 2^n-2^k (avec ^ pour puissance), en non signé. Sinon, il n'était pas si difficile de songer que 1—10—0 = 1—1 - 0—01—1 et de vite retrouver le même résultat. Pour ceux qui se sont aventurés, en dépit de l'avertissement, dans le calcul de la série, que de manque de rigueur dans les valeurs des bornes et dans ce calcul pour lycéen... Sinon, l'arithmétique modulo 2^n fait que, pour un code donné de MSB 1, l'entier signé correspondant se trouve 2^n sous l'entier non signé, cf. CM2/P28 ou P29. D'où -2^k ici. |

| 5 |

1

|

L'implication est l'ordre partiel fondamental sur lequel repose

l'algèbre de Boole. L'implication fonctionnelle f=>g doit être vérifiée en chaque point de B^n, cf. CM2/P13. Sur B^3, "ab" compte 2 '1', inclus dans

les 4 '1' de "c'a+cb". Donc cet "intervalle fonctionnel" est non vide et comporte, hors ses bornes, 2 fonctions à 3 '1'... |

2

|

6a |

1

|

Electrons pour nMOS, trous (rien à voir

avec la notion, statique, de lacune) pour pMOS. |

| 6b |

1

|

Le signe d'une charge soumise à un champ électrique n'a aucune influence sur le sens du courant électrique que son mouvement fait apparaître. Par contre, sa mobilité, oui, et, justement, celles des électrons et trous sont différentes, d'un facteur presque 3 en faveur des électrons. |

| 7 |

1

|

cf. CM3/P17, ou bien l'énoncé n°2 de la page wikipédia

correspondante. Ce n'est pas la puissance de calcul qui double ! |

| 8 |

1

|

2 inverseurs CMOS rebouclés (ou tête-bèche), montage dont l'intérêt principal est de constituer un dispositif bistable, cf. CM5/P5&P27, élément mémorisant fondamental, alias "cellule mémoire". |

| 9 |

1

|

Entre 10 et 100 milliards actuellement, cf. CM3/P19. |

| 10 |

1

|

cf. CM7/P23, en bas. La question n'est pas "Quelle différence entre CD et UC ?" mais entre les bascules qui sont dedans... |

| 11a |

1

|

Instruction qui porte l'un de ses opérandes dans son propre code (en tant que valeur immédiate), au lieu d'indiquer le registre où aller le chercher, d'où une économie d'un registre, cf. CM9/P17. |

| 11b |

1

|

L'instruction jr (j pour saut) a pour argument un registre (ra, généralement) dans lequel on trouve l'adresse de l'instruction que le processeur devra charger et exécuter au prochain cycle d'horloge. Elle est indispensable pour les retours de sous-programmes, le registre ra ayant justement reçu préalablement l'adresse de retour, au moment de l'appel (par jal), cf. CM9/P26. |

| 12 |

1

|

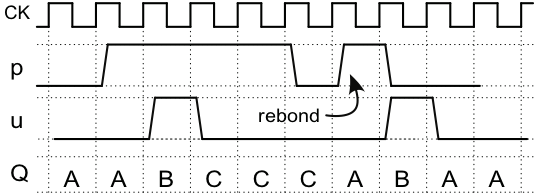

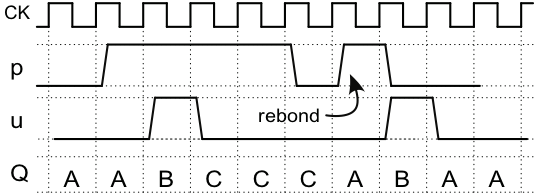

Pour exploiter un signal asynchrone en entrée d'un circuit séquentiel séquencé par l'horloge CK, on le fait d'abord passer par une bascule D pilotée par la même horloge. Et on utilise ensuite uniquement cette seule version "synchronisée" de p, cf. CM6/P4. Cette précaution est naturellement supposée prise ici pour la suite du problème. |

| 13 |

1

|

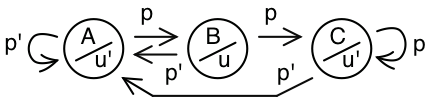

cf. PC6/Q2c. Les transitions rebouclant sur chaque état sont essentielles pour la complétude du DE (c'est d'ailleurs elles qui vont être le plus utilisées). L'entrée p n'a rien à faire à l'intérieur des cercles, correspondant aux états. |

3

|

14a |

1

|

Clignotement de l'ampoule (qui en souffrira peut-être, quoique, pas de pb avec le 50Hz du secteur...) au rythme haute fréquence de l'horloge pendant l'appui sur le bouton-poussoir, et donc résultat aléatoire au relâchement, donc un tel télérupteur est inutilisable en pratique. |

| 14b |

1,4 |

Travail plus simple qu'en CM7/P17 ou PC7/Exo2, plutôt similaire à CM6/P14 mais dans le sens de la synthèse, donc du haut vers le bas. Aboutit à la loi de transition q+ = q⊕p et à la loi de sortie a=q. Il apparaît que le concept de représentation d'état, pourtant introduit à la fois en AO102 et ES102, n'est toujours pas clair chez nombre d'étudiants : tous ceux pour qui faire apparaître le bit d'état q n'est pas naturel. Il était cependant légitime ici de considérer la sortie binaire a comme bit d'état (justifiant alors la notation a+) à condition de le dire explicitement. D'autre part, pour l'implantation en portes, on ne se prive pas d'être plus concis que la FDM, d'où utilisation d'une simple porte XOR comme bloc de transition. Enfin, bascule D et sortie sont indispensables à l'implantation. |

| 14c |

1

|

24 transistors pour une bascule D (cf. CM6/P3) et 12 pour un XOR (cf. PC4/Q1e), d'où 36 au total. |

| 15a |

1,4

|

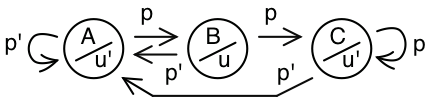

Déjà abordée artisalement/astucieusement en PC6/Q1b, par exploitation d'un registre à décalage, la détection synchrone de transition montante est ici revisitée de façon plus fondamentale, donc avec nécessité d'exprimer le comportement souhaité sous forme d'un diagramme d'état (cf. PC8/Exo1), avec des états symboliques. Un tel DE comporte forcément au moins 3 états, l'un "transitoire" avec sortie u=1, les deux autres avec sortie u=0 selon que le bouton est durablement appuyé ou relaché. Le DE ci-dessous ne fait pas d'hypothèse sur la durée d'appui et fonctionnerait même si p était à 1 un top d'horloge sur 2 (valant à ses auteurs le bonus du 9ème point). Un DE pour lequel l'entrée p durablement à 1 provoque un cycle sur plusieurs états est généralement archi-faux (a minima sous-optimal).

|

| 15b |

1 |

4

|

16 |

1

|

Pour ignorer un phénomène durant jusqu'à 50 cycles d'horloge, il faut un compteur de largeur n=6. Pas besoin de calculette pour calculer un log. en base 2 ! |

| 17a |

1 |

Ce n'est pas c_n qu'il faudrait relier à c_0, mais son complément, afin que l'incrémentation cesse quand le compteur s'apprête à déborder (c'est-à-dire retourner à 0). Mais cela constituerait une boucle combinatoire, situation que l'on a exclue, vu ses dangers, cf. CM5/P5. |

| 17b |

1

|

Au lieu de s'appuyer sur c_n pour détecter le débordement imminent, on calcule le ET de tous les bits d'état q_i et on branche le complément sur c_0 : pas de boucle combinatoire dans ce cas. |

| 17c |

1 |

Il s'agit ici d'achever la réalisation de la détection de transitions montantes hors rebond décrite en fin de page 3. Or à la question précédente, l'entrée p n'intervient plus, ce qui est troublant. Mais p doit aussi jouer le rôle d'un reset et ce rôle suffit, en fait. Il demande juste une porte ET en amont de chaque bascule du compteur. Enfin, il ne faut pas oublier la sortie u. On obtient celle-ci par un ET sur tous les bits d'état, sauf sur q_0 dont il faut prendre le complément. Cela est mutualisable avec le ET de la question précédente. |

| 18ab |

2 |

a'+b'+c', a'b'+c', a'b'+a'c' et a'.b'.c' (toutes sous FDM bien sûr) qui s'implantent sans inverseur, ainsi que ab et a+b, qui ont besoin d'un inverseur en sortie, ainsi encore que a'b et a'+b, qui ont besoin d'un inverseur en entrée. Et c'est finalement a'b'+c' qu'il fallait dessiner. Deux intrus enlevaient un point. |

| 19 |

1

|

Série de 3 inverseurs rebouclés, constituant un oscillateur en anneau. S'ils ne sont pas rebouclés, cela revient à un simple inverseur, en un peu plus lent :-( |

5

|

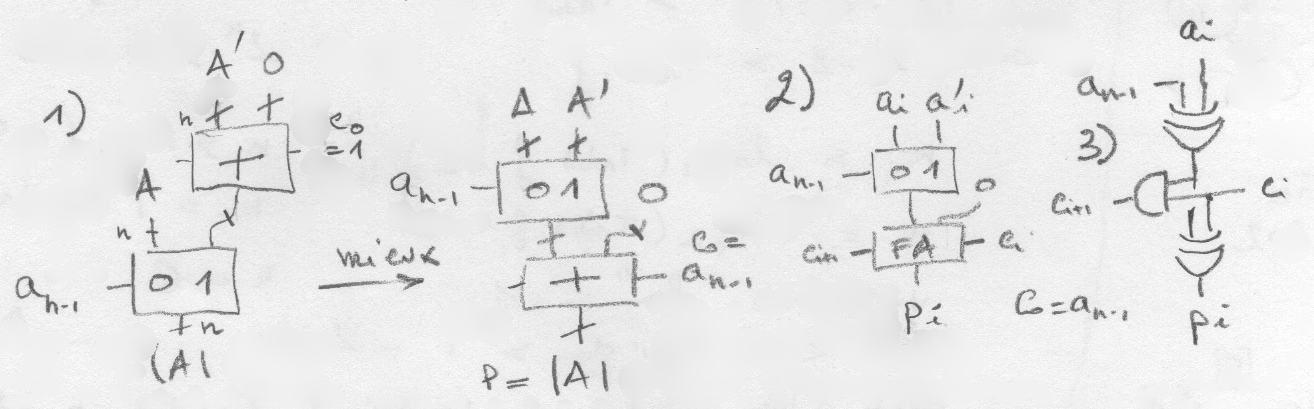

20ab |

2

|

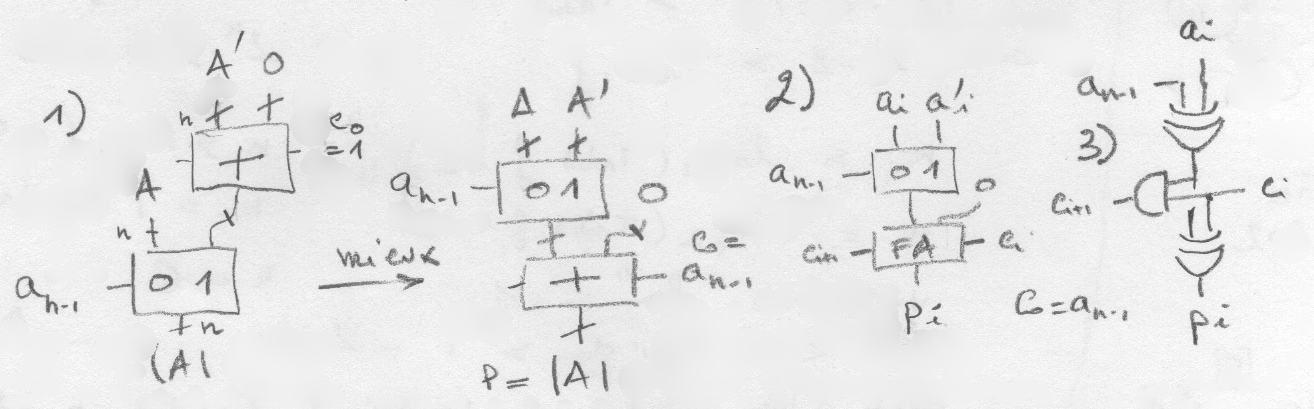

Utilisons la notation multiplexeur (a?b:c) du langage C pour b si a, sinon c. Alors les schémas demandés sont équivalents aux formules suivantes.

1) (a_n-1 ? A'+1 : A), donc nécessité aussi d'un additionneur avec c_0=1

ou, mieux, (a_n-1 ? A' : A ) + a_n-1 car le MUX va se simplifier en XOR, mais alors il faut c_0=a_n-1 sur l'additionneur

2) FA avec entrées 0 et (a_n-1 ? a_i' : a_i ) et c_0=a_(n-1) à l'entrée du premier

3) le FA se simplifie en AND+XOR comme dans un compteur et (a_n-1 ? a_i' : a_i ) en un XOR aussi : a_(n-1)⊕a_i

Mais c'est bien sûr sous forme de schéma que les réponses étaient attendues :

|

| 20c |

1

|

La valeur absolue de -2^(n-1) est +2^(n-1), qui ne fait pas partie des entiers signés exprimables sur n bits. Avec n bits (la valeur de n a un caractère matériel, donc ne se modifie pas), la seule solution est donc de l'exprimer en tant qu'entier non signé. Les autres entiers ne sont pas concernés. Bref, si vous faîtes un calcul de valeur absolue dans un code C destiné à être embarqué à bord d'une Ariane ou d'un Airbus, il va falloir faire attention à ce que vous écrivez : vous ne voudriez pas qu'elle/il risque de se "planter" à cause de ça ? |

| 20d |

1

|

C'est le principe de l'addition à retenue propagée qui a été implicitement retenu ci-dessus, d'où une complexité temporelle en O(n). Mais la chaîne des retenues réalise en fait un calcul de ET-préfixe (cf. CM8/P10) dont on sait qu'il est parallélisable en temps logarithmique. Et on ne peut pas faire mieux, d'après le théorème de Winograd. |